奧林巴斯顯微鏡:CCD像素偏移技術

像素偏移技術是用來結合收集到的電荷由幾個相鄰的CCD像素時鐘方案,旨在降低噪聲和提高信號噪聲比和幀速率的數碼相機。由芯片上的的CCD時鐘定時電路,假定控制的串行和并行的移位寄存器的CCD模擬信號的放大前進行了分塊的過程。

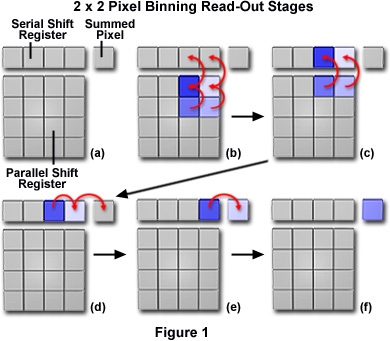

為了幫助說明像素偏移技術過程,請參閱圖1,檢討例如2×2分級。甲示意圖一個4×4并行移位寄存器的像素陣列,在圖1(a)所示,伴隨著四門的串行移位寄存器,加法像素或(也稱為一個輸出節點)。照明光子影響CCD光電二極管,建立電子池的積累在每個像素中,在圖1(b)所示為一個群集并行移位寄存器在右上角的四個藍色陰影廣場。每個像素可容納的電子的數量被稱為阱的深度和范圍從約30,000至350,000,取決于CCD式樣。的CCD的動態范圍是成正比阱的深度。入射光水平和曝光時間確定在每個photogate或像素站點收集的電子數。一個光照周期的CCD的曝光完成后,電子轉移通過并行和串行移位寄存器的輸出放大器,然后由模擬到數字(A / D)轉換器電路的數字化。離散化,可以使用提高對焦精度,減少了所需的時間進行圖像采集,同時提供更高的靈敏度降低的離焦光的水平。

為了說明這個過程中,圖1(b)示出各集成電路的像素在并行寄存器步進增量的一個柵極,得到圖1(c)中所示的布置。在這里,從兩個像素的電子保持在并行移位寄存器,而從其他兩個已轉移至串行移位寄存器。的另一個步驟(圖1(c)),在并行移位寄存器在串行寄存器(圖圖1(d)),填充相鄰柵極元件的其余電子轉移。最后的步驟涉及從串行寄存器的電荷轉移,兩個像素在同一時間,求和像素(圖圖1(d)及(e))。圖1(g)示出的4個像素的總電量在總結以及等待傳送到輸出放大器,信號將被轉換為電壓,然后轉移到其它集成電路進一步放大和數字化。這個過程一直持續,直到整個陣列已被讀出。在這個例子中,4個相鄰的像素的區域的已結合成一個較大的像素,有時被稱為“ 超級像素。該signal-to-noise比已增加了四倍,但圖像的分辨率被削減了50%。

像素偏移數組的大小的控制由CCD時鐘,偏置電壓,和視頻處理信號的時序,并且通常用來調節到最大,可以包括幾乎整個CCD陣列的2×2像素。然而,在分級模式中,串行移位寄存器和輸出節點將積累了顯著較大的電荷比正常運行,必須含有足夠的電子電荷量,以防止飽和。典型的CCD串行寄存器的兩倍的充電容量為并行寄存器,和輸出節點通常含有50 - 100%的充電容量比的移位寄存器。作為一個例子,柯達KAF全幀CCD圖像傳感器9微米像素的平行陣列,每個具有一個容量為12萬個電子。的KAF串行寄存器有兩倍的并行寄存器(24萬個電子)的電子的能力,而在輸出節點有一個容量為33萬個電子。

像素偏移技術的主要優點是在低光照條件下以犧牲空間分辨率提高信號噪聲比。許多電荷包的求和時間讀出的噪聲電平,并產生一個信號等于使用了分塊的系數(在上面的例子4)改善。暗電流噪聲分級和不降低,可能只克服了低溫的冷卻CCD。離散化的各種應用中是有用的,特別是在快速的通過時間(幀速率)是理想的犧牲分辨率。